设有如下图所示的单总线[1]结构,分析指令ADD(RO),R1((RO))+(R1)-(RO)]的 令流程和控制信号。控制信号 ·..若令译码/控制器-|||-IR-|||-IRin 总线-|||-AdIRout-|||--PCiny-|||-PC-|||-MemR→ 主 MAR MA-|||-MARout-|||-存 →MDRoutE-|||-MemW- MDRinE ut-|||-MDR-|||-ROin-|||-R-|||-Roout-|||-_(0)-1 -1n-|||--10(1t)-|||-square Yin-|||-ALUIn-|||-控制信号一 ALU-|||-z Zout

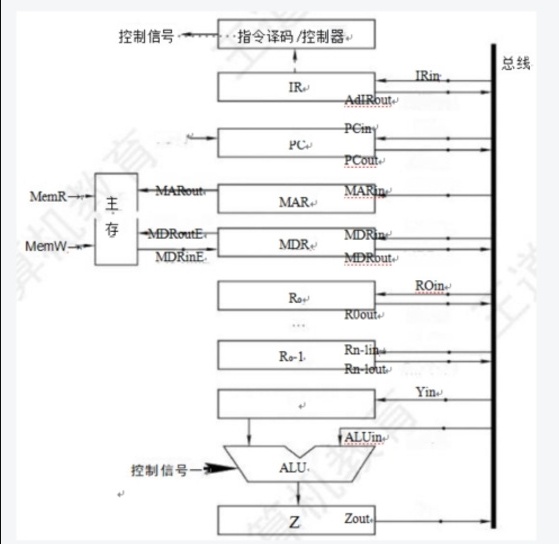

设有如下图所示的单总线[1]结构,分析指令ADD(RO),R1((RO))+(R1)-(RO)]的 令流程和控制信号。

题目解答

答案

指令分析

对于指令ADD(RO),R1(假设这里的含义是将(RO)所指向的存储单元[2]内容与R1的内容相加,结果存回(RO)所指向的存储单元)。

指令流[3]程和控制信号

取指阶段:

控制信号PC - > ABUS有效,将程序计数器[4]PC的值送到地址总线[5]ABUS上,以便从存储器[6]中取出指令。

控制信号MEMR(存储器读信号[7])有效,使存储器根据地址总线上的地址读取指令,并将指令送到数据总线[8]DBUS上。

控制信号DBUS - > IR有效,将数据总线上的指令送到指令寄存器[9]IR中。

同时,PC自动加1,为取下一条指令做准备。

指令译码阶段:

指令寄存器IR中的指令被译码,识别出这是一条加法指令,并且操作数[10]一个是(RO)所指向的存储单元内容,另一个是R1的内容。

控制信号RO - > ABUS有效,将寄存器[11]RO的内容送到地址总线ABUS上,以便从存储器中读取(RO)所指向的存储单元内容。

控制信号MEMR再次有效,根据ABUS上的地址从存储器中读取数据到DBUS上。

控制信号DBUS - > TEMP有效(假设存在一个临时寄存器TEMP),将从存储器中读取的数据暂存到TEMP寄存器中。

执行阶段:

控制信号R1 - > ALU和TEMP - > ALU有效,将寄存器R1的内容和临时寄存器TEMP的内容送到算术逻辑单元[12]ALU进行加法运算。

控制信号ALU - > DBUS有效,将ALU的运算结果送到数据总线DBUS上。

控制信号DBUS - > MEM(存储器写信号)有效,同时RO - > ABUS再次有效,将DBUS上的结果写回[13]到(RO)所指向的存储单元中.

解析

取指阶段的主要任务是从存储器中取出指令。首先,程序计数器PC的值被送到地址总线ABUS上,以便从存储器中取出指令。然后,存储器读信号MEMR有效,使存储器根据地址总线上的地址读取指令,并将指令送到数据总线DBUS上。最后,数据总线上的指令被送到指令寄存器IR中。同时,PC自动加1,为取下一条指令做准备。

步骤 2:指令译码阶段

指令译码阶段的主要任务是识别指令类型和操作数。指令寄存器IR中的指令被译码,识别出这是一条加法指令,并且操作数一个是(RO)所指向的存储单元内容,另一个是R1的内容。然后,寄存器RO的内容被送到地址总线ABUS上,以便从存储器中读取(RO)所指向的存储单元内容。存储器读信号MEMR再次有效,根据ABUS上的地址从存储器中读取数据到DBUS上。最后,数据总线上的数据被送到临时寄存器TEMP中。

步骤 3:执行阶段

执行阶段的主要任务是执行指令。寄存器R1的内容和临时寄存器TEMP的内容被送到算术逻辑单元ALU进行加法运算。ALU的运算结果被送到数据总线DBUS上。存储器写信号MEMW有效,同时寄存器RO的内容再次被送到地址总线ABUS上,将DBUS上的结果写回到(RO)所指向的存储单元中。