某机器中,已知配有一个地址空间为0000H~3FFFH的ROM区域。现在再用一个RAM芯片(8K×8)形成40K×16位的RAM区域,起始地址为6000H。假设RAM芯片有CS’和WE’信号控制端。CPU的地址总线为A15~A0,数据总线为D15~D0,控制信号为R/W(读/写),MREQ’(访存),要求:(1)画出地址译码方案。(2)将ROM和RAM同CPU连接。

某机器中,已知配有一个地址空间为0000H~3FFFH的ROM区域。现在再用一个RAM芯片(8K×8)形成40K×16位的RAM区域,起始地址为6000H。假设RAM芯片有CS’和WE’信号控制端。CPU的地址总线为A15~A0,数据总线为D15~D0,控制信号为R/W(读/写),MREQ’(访存),要求:

(1)画出地址译码方案。

(2)将ROM和RAM同CPU连接。

题目解答

答案

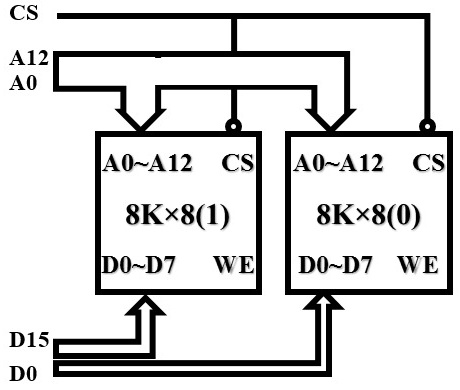

解:RAM区域共需RAM芯片40K×16/8K×8=10片,可先用2片8K×8位的RAM芯片用于位扩展构成8K×16位存储器,然后再用5组8K×16位存储器用于字扩展构成40K×16位存储器,该存储器的组成逻辑框图可参照5、6题。

(A)为了将ROM和RAM同CPU连接,需先将十六进制地址转换为二进制地址码,并确定ROM容量,以及观察ROM和RAM地址码的特点。

A15~A12 | A11~A8 | A7~A4 | A3~A0 | 说明 |

0000 | ROM,16K×16 | |||

... | ... | ... | ... | |

1 | 1111 | |||

0000 | 空区域 | |||

... | ... | ... | ... | |

1 | 1111 | |||

0000 | RAM(0),8K×16 2片8K×8位扩展 | |||

... | ... | ... | ... | |

1 | 1111 | |||

1 | 0000 | RAM(1),8K×16 2片8K×8位扩展 | ||

... | ... | ... | ... | |

1 | 1111 | |||

1 | 0000 | RAM(2),8K×16 2片8K×8位扩展 | ||

... | ... | ... | ... | |

1 | 1111 | |||

11 | 000 | RAM(3),8K×16 2片8K×8位扩展 | ||

... | ... | ... | ... | |

11 | 111 | |||

111 | 00 | RAM(4),8K×16 2片8K×8位扩展 | ||

... | ... | ... | ... | |

1111 | 1111 | 1111 | 1111 |

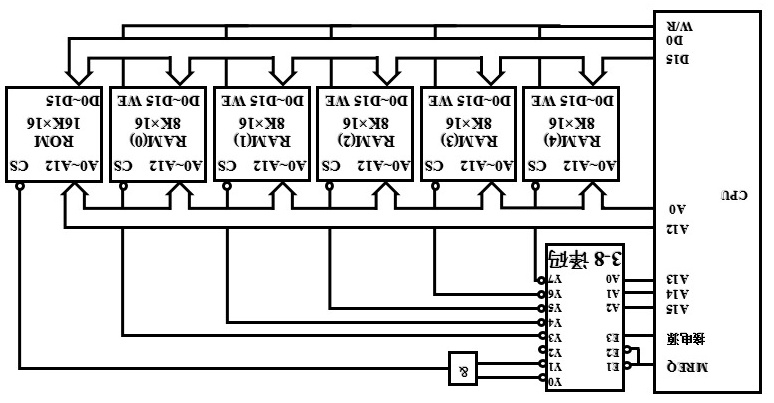

(B)分配CPU地址线:将CPU的低13位地址A12~A0与ROM和2片8K×8位RAM的地址线相连。剩下的高位地址A13~A15与访存信号共同产生芯片的片选信号。

(C)片选信号的形成:观察上面的地址码发现,当访存信号MREQ’=0,而且高位地址A13~A15为000(或001)、011、100、101、110、111时,分别选择ROM、RAM(0)、RAM(1)、RAM(2)、RAM(3)和RAM(4)芯片,故,可采用一个3-8译码器来实现上述片选关系,最后得ROM和RAM与CPU的连接如下图所示。

解析

RAM区域共需RAM芯片40K×16/8K×8=10片,可先用2片8K×8位的RAM芯片用于位扩展构成8K×16位存储器,然后再用5组8K×16位存储器用于字扩展构成40K×16位存储器,该存储器的组成逻辑框图可参照5、6题。

步骤 2:分配CPU地址线

将CPU的低13位地址A12~A0与ROM和2片8K×8位RAM的地址线相连。剩下的高位地址A13~A15与访存信号共同产生芯片的片选信号。

步骤 3:片选信号的形成

观察上面的地址码发现,当访存信号MREQ’=0,而且高位地址A13~A15为000(或001)、011、100、101、110、111时,分别选择ROM、RAM(0)、RAM(1)、RAM(2)、RAM(3)和RAM(4)芯片,故,可采用一个3-8译码器来实现上述片选关系,最后得ROM和RAM与CPU的连接如下图所示。