题目

某主存系统中,其地址空间0000H~1FFFH为ROM区域,ROM芯片为8K×8位,从地址6000H开始,用8K×4位的SRAM芯片组成一个16K×8位的RAM区域,假设RAM芯片有和信号控制端。CPU地址总线为A15~A0,数据总线为D7~D0,读/写控制信号为R/,访存允许信号为,要求:(1)写出地址译码方案;(2)画出主存与CPU的连接图。

某主存系统中,其地址空间0000H~1FFFH为ROM区域,ROM芯片为8K×8位,从地址6000H开始,用8K×4位的SRAM芯片组成一个16K×8位的RAM区域,假设RAM芯片有和信号控制端。CPU地址总线为A15~A0,数据总线为D7~D0,读/写控制信号为R/,访存允许信号为,要求:

(1)写出地址译码方案;

(2)画出主存与CPU的连接图。

题目解答

答案

(1)地址译码方案如下:

将地址的高3位A15、A14、A13经3:8译码器74LS138译码后实现片选,具体连接如下:

将 作为8K×8位ROM的

作为8K×8位ROM的 ;

;

将 、

、 分别作为2组8K×8位RAM的

分别作为2组8K×8位RAM的 ;

;

)

将3:8译码器74LS138的一个使能端 与CPU发出的访存允许信号

与CPU发出的访存允许信号 相连,其它两个使能端、

相连,其它两个使能端、 置均为无效信号。

置均为无效信号。

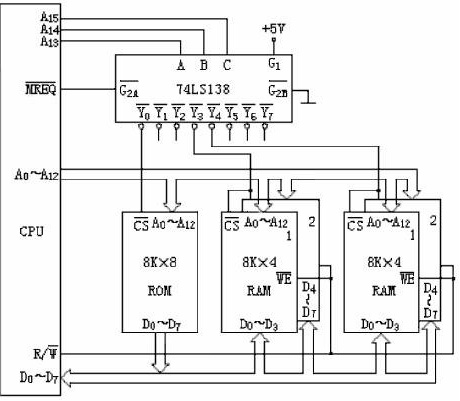

(2)主存与CPU的连接图如附图所示。

附图 主存与CPU的连接图

解析

本题考查存储器地址分配与译码设计以及存储器与CPU的连接。

核心思路:

- 地址译码:利用高位地址(A15~A13)通过译码器(74LS138)产生片选信号,区分ROM和RAM区域。

- 存储器扩展:通过并联SRAM芯片实现数据位扩展,通过地址扩展实现容量扩展。

关键点:

- ROM区域(0000H~1FFFH)需唯一片选信号。

- RAM区域(6000H~7FFFH)需两片8K×4位SRAM并联组成16K×8位,需两组片选信号。

- 译码器使能:通过访存允许信号$\overline{MEFQ}$控制译码器有效。

(1) 地址译码方案

- 高位地址分配:

- ROM区域(0000H~1FFFH)对应A15=0, A14=0, A13=0~1。

- RAM区域(6000H~7FFFH)对应A15=1, A14=1, A13=0~1。

- 译码器配置:

- 74LS138输入端接A15、A14、A13。

- 使能端$\overline{MEFQ}$接G2A,G1和G2B置无效(G1=0, G2B=1)。

- 片选信号:

- Y0:选中ROM(0000H~1FFFH)。

- Y1、Y2:分别选中两组SRAM(6000H~7FFFH)。

(2) 主存与CPU连接

- 地址总线:

- ROM和SRAM的地址输入接A0~A12。

- 数据总线:

- ROM数据输出接D7~D0。

- SRAM分两组:一组接D0~D3,另一组接D4~D7。

- 控制信号:

- ROM片选$\overline{CS}_{ROM}$接Y0。

- SRAM片选$\overline{CS}_{RAM1}$、$\overline{CS}_{RAM2}$分别接Y1、Y2。

- 读写控制$\overline{R/W}$接CPU的$\overline{R}$。